하드웨어 파보기(1) - 메모리 계층 구조

가산 장치인 CPU는 우리가 알고 있는 컴퓨터의 뇌, 연산 장치입니다. 이는 엄청난 연산 속도를 갖고 있으며 기술이 고도화 되며, 유저가 갖고 있는 서비스에 대한 기댓값을 충족 시키기 위해 최신 기술은 CPU가 얼마나 더 빠른 연산을 해내는가에 초점이 맞춰져 있을 것입니다.

CPU는 크게 봤을 때 RAM에 데이터를 임시로 올려 이를 연산합니다. 즉, 예를 들면 보조 기억 장치 등에 저장 되어 있던 데이터를 RAM에 올리는 것이죠. 그런데 여기에서 자세히 들어가면 메모리는 계층 구조를 갖고 있습니다. 이 구조는 왜 만들어졌으며, 어떠한 구조를 갖고 있을까요?

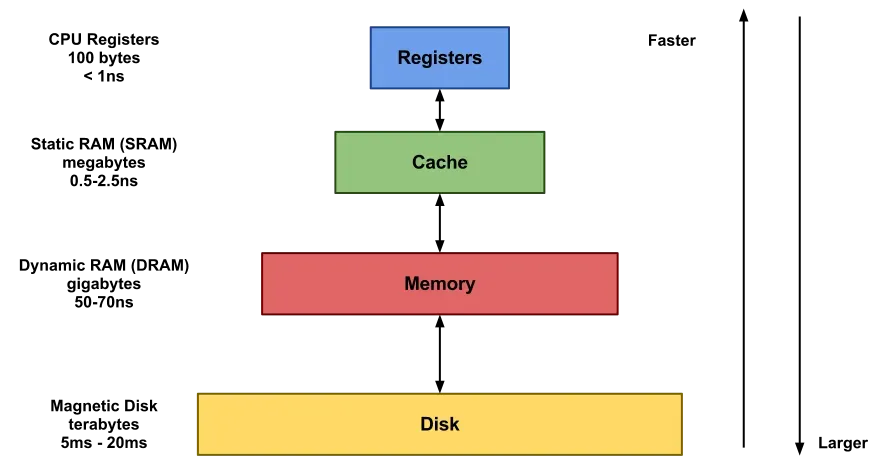

메모리 계층 구조는 크게 다음과 같습니다.

- Register(SRAM)

- Cache(SRAM)

- Main Memory(RAM, DRAM)

- Secondary memory(HDD, SSD)

하드웨어 파보기(2) - CPU가 연산하는 과정, 왜 Register는 RAM보다 빠른가?

CPU는 가장 가까이에 있는 메모리인 Register에 저장된 데이터를 연산하며, 추가적으로 Cache도 존재하여 연산 대상이 될 예정인 데이터도 저장하고 있죠. 이들은 기존에 주 기억 장치인 RAM에 올라갔던 데이터들일 것입니다. 또는 파일에 존재했던 데이터라면 보조 기억 장치인 HDD나 SSD에 저장 되어 있던 데이터를 IO 컨트롤러가 이를 가져와 RAM에 올리는 과정을 거쳤겠죠. 이때 왜 Register, Cache, Main memory(RAM), Secondary memory에 대한 계층 구조가 있고, 이들은 어떠한 차이가 있는지 알아봤습니다.

결국 가장 빠른 것은 Register입니다. CPU는 왜 RAM에 있는 데이터를 바로 가져와서 연산하는 것이 아닌 Cache에 올려서 스케줄러의 명령을 기다리다 순서가 되었을 때 Register에 올리고 이를 연산할까요? 이유는 두 가지입니다.

- 물리적인 거리 및 위치

- 둘의 재료 및 구성품의 차이 (SRAM, DRAM)

첫 번째 이유로 Register와 RAM은 CPU와 물리적인 거리가 다릅니다. 정확히 따지면 ALU와의 거리겠죠. CPU의 구성 요소로는 크게 Control unit, ALU, Register로 나뉘고 추가로 Cache가 존재합니다. 즉 Register는 연산을 할 ALU의 가장 가까이에 있는 메모리로 물리적으로 가장 빠르게 전기 신호를 전달 할 수 있습니다. 반면에 주 기억 장치인 RAM은 메인 보드에서 CPU와 다른 공간에 꽂혀서 시스템 버스를 통해 신호를 주고 받습니다.

두 번째 이유로는 둘의 재료 및 구성품의 차이가 있습니다. RAM은 DRAM, Register와 Cache는 SRAM으로 만들어집니다. D와 S는 각각 Dynamic과 Static입니다. 동적이고 정적인 차이라면 무엇이 변하고 무엇이 변하지 않을까요? 바로 저장하고 있는 전하입니다.

하드웨어 파보기(3) - RAM(DRAM), Register(SRAM)의 차이

DRAM은 지속적으로 전하를 저장하지 못하고 데이터를 저장하는데 계속 Refresh를 하는 과정이 있어 속도가 느립니다. DRAM이 전하를 지속적으로 저장하지 못하는 이유는 두 가지입니다.

- 완벽한 절연체란 없기 때문에 전자가 누출된다.

- 공정이 나노 단위로 매우 작아지며 서로 간격이 짧아진다. 이로 인해 전자 단위까지 영향을 끼치며 이 상황에서 전자의 누출이 발생된다.

DRAM은 전하를 일정하게 유지할 수 없는 구조로 되어 있어 지속적으로 Refresh하는 구조입니다. 이유는 DRAM은 수 십억 개의 Capacitor, Transister를 갖고 있고, 단위 당 즉, 1 Bit를 표현하기 위해 Capacitor와 Transistor 하나 씩으로 이루어져 있는 구조이기 때문입니다.

Capacitor는 전하를 저장하는 저장소이고, Transistor는 스위치입니다. 이때 Capacitor에 전원을 연결하면 Capacitor 내부에 있는 전자 펌프가 동작합니다. +극에 연결된 도체에 있는 전자가 -극에 연결된 도체로 이동하는 것이죠. 펌프의 역할이 끝나고, 펌프의 통로를 막는다면 두 도체 사이에는 절연체가 있어 에너지는 갖고 있지만 움직일 수 없는 긴장된 상태가 됩니다. 이로써 에너지를 갖게 되죠. 하지만 이 세상에 완벽한 절연체는 없기 때문에 지속적으로 전자는 누출되게 됩니다. 에너지를 갖게 되는 이유는 열역학 제 2법칙, 엔트로피 증가 법칙으로 에너지는 무조건 무질서한 방향으로 움직이기 때문에 전자가 더 퍼지려 합니다. 좀 더 이야기 하면 전자가 모임으로써 전자가 같은 공간에 더 많이 생겼으므로 이를 해소하고 더 자유로워지고 싶기 때문에 에너지를 갖습니다.

이에 반해 Regiser와 Cache가 이루어진 SRAM은 1 Bit를 표현하기 위해 6개의 Transistor로 구성 되어 있고, 두 개 씩 짝을 짓는다고 합니다. 이것은 Inverter(인버터)라고 합니다. 네 개의 트랜지스터는 2개의 인버터로써 짝을 짓고, 0 또는 1을 나타내며 이를 저장할 수 있고, 나머지 두 개의 트랜지스터는 전류의 흐름을 제어하는 스위치 역할을 합니다. 여기에서 전하를 갖는 방식은 Transistor 하나가 1을 갖고 싶다면 짝을 지은 나머지 하나의 Transistor가 0의 전하를 갖기 위해 전류를 계속 내보내야 합니다. 이로써 DRAM 보다 더 많은 전류를 내보내야 하며, DRAM과 다르게 지속적으로 전류를 내보내기 때문에 전류가 멈추지 않는 이상 일정한 전하량을 갖게 됩니다.

그럼 이렇게 물어볼 수 있습니다. ‘DRAM도 SRAM처럼 동일하게 전류를 계속 내보내서 캐퍼시터의 전하량을 일정하게 맞추면 되는 거 아니야?’ 하지만 이렇게 하는 것은 DRAM의 높은 집적도(작은 크기)와 가격적인 이점을 포기하는 것입니다. SRAM은 지속적인 전류를 유지하기 위해 두 개의 트랜지스터 등을 추가하여 이를 만들었습니다. DRAM은 굳이 이러한 장치를 해도 SRAM 보다 나은 위치에 있을 수 없습니다. 그래서 가격적, 작은 크기에 대한 이점을 가져가고, 속도를 잃는 것이죠.

이렇게 각자의 장단점으로 각 계층에서 각자의 역할을 하게 됩니다. 그런데 개발자가 메모리 계층에서 시작해서 열역학 제 2법칙까지 왔네요. 여기 레벨까지 오는 게 맞을까요? ㅎㅎ.. 어찌 오다 보니까 깊게 와봤네요. 그래도 컴퓨터 구조 레벨에서 데이터는 어떻게 저장 되는지, 왜 메모리 계층 구조를 가지며 서로 속도가 차이 나는지 알아봤습니다.

'개발 일지' 카테고리의 다른 글

| HTTP'S'에서 S를 떼어내어 작동 방식을 조금 더 파보았다 (1) | 2025.09.20 |

|---|---|

| 오픈소스 컨트리뷰션 아카데미(OSSCA) 참여형 Challenges 후기 (6) | 2025.08.11 |

| 제 5회 프로그래머스 데브 코스 커리어 TALK, 취업을 앞당기는 실전 전략과 취업 인사이트 후기 (0) | 2025.07.07 |

| socket.io의 특징과 장단점 (0) | 2024.08.02 |

| socket.io 서버 소켓에서 연결된 클라이언트 소켓 ID와 입장한 room을 찾는 방법 (0) | 2024.08.02 |